北京时间2018年7月11日凌晨,ARM发言人承认了质疑RISC-V架构的网站(http://riscv-basics.com)确实是ARM发布的,“本意是为了增进大家讨论芯片架构,而不是恶意攻击RISC-V”,并且宣布已经将该网站下线。

但战火并没有停止,在很多硬件或开源技术社区里,有关RISC-V和ARM的辩论依旧激烈。

作为一个物联网爱好者,肯定会好奇为什么 RISC-V 会让如日中天的ARM这么紧张?

那么多挑战者,不是都没掀起大浪吗?

这个事情还得从头说起。

××××××××××××××××××

最早的时候大家整天被“等灯、等灯”的Intel广告洗脑,我们的PC和服务器也大多使用Intel或AMD的x86处理器来运行我们的程序。

移动时代来临之后,精简指令集的ARM仰仗自己的低功耗和低成本,迅速在手机和平板等终端确立了霸主地位。 华为、高通、Samsung、苹果等大厂都在基于ARM做着自己的软硬件产品。

目前,ARM占据全球移动通讯领域90%的市场,而且还把触角伸向了企业基础架构以及人工智能两大领域。

ARM和x86两大阵营互相攻伐,几乎无视第三方竞争者。

可是过了一段时间,大家发现IoT时代到了!新需求又来了!

如果把当前的阶段当作IoT时代的初期,ARM依然有着强大的优势,不管是架构还是工具链、系统、应用……

但领先的玩家已经把目光放到了IoT时代的中期,在他们的视角里,万物互联的时代,CPU必须结构更简单,性价比更高。很明显,ARM在那个时候可能会力不从心。

为什么会这么说?

1、复杂度已经大幅提高

作为商用架构,要保持向后兼容性,不得不保留许多过时的定义,导致其指令数目多,指令冗余严重,文档数量庞大,所以要在这些架构上开发新的操作系统或者直接开发应用门槛很高。

如果把ARM和x86的架构文档做个对比,就能发现复杂度快差不多了。为了保持兼容度,提高安全性,提高性能……ARM不得不承载过多的“背负”,慢慢变得有点像它以前讨厌的样子。

2、授权费不便宜

ARM虽然开放,但并不开源。ARM公司本身并不靠自有的设计来制造或出售CPU,而是将处理器架构授权给有兴趣的厂家。ARM 提供了多样的授权条款,包括售价与散播性等项目。

ARM授权方式主要有三种:架构层级授权、内核层级授权、使用层级授权。价格根据客户要求有高有低。授权条款虽然比Intel好一些,但也仅仅是好一些而已。ARM在指令集授权上非常吝啬,获得ARM32授权的公司一只手都能数的过来,ARM64授权虽然多,但授权费却异常昂贵,法国芯片创业公司Greenwave表示,他们如果使用ARM架构,要花掉1500万美元的授权费。而且授权到期后,是否继续授权和授权费用都要重新谈判。

物联网时代的芯片要有什么特点?

芯片是实现物物相连的关键,物联网的芯片偏重于解决低功耗、高整合度,低功耗连接使开发人员能够为功耗受限的设备添加更多功能,同时保持尺寸小巧,从而扩大了其应用可能性。添加集成度越来越高的元件,通过即插即用方案简化新应用的开发,快速将新设备推向市场。

以上这段是用ARM的设备商用来捧ARM的,但却恰恰说到了物联网时代的芯片关键。

ARM可能部分符合这段文字,但当前最符合这段文字的,可能是我们接下来要说到的 —— RISC-V。

RISC-V读作RISC Five,意思是第五代精简指令处理器。取这个名字只是因为美国伯克利研究团队的David Patterson教授在此之前已经研制了四代精简指令处理器芯片。

RISC-V有什么可取之处?

1、授权更开放,更宽松。

作为ARM的同门师弟(ARM和RISC-V都是精简指令集),RISC-V并不是第一个开源芯片架构。

在它之前,还有一个雷声大,雨点小的OpenRISC。由于采用了GPL和LGPL作为其开源协议(其中硬件设计采用LGPL,而模型和固件采用GPL)。让大部分商业公司望而却步,发展缓慢。

为了吸取OpenRISC的教训,RISC-V采用了BSD协议,这个协议的要求非常宽松,没有任何限制包括闭源和商用。很显然,RISC-V采用这个协议是为了吸引更多的人和公司参与到社区和生态的建设当中。当然,BSD协议本来就是Berkelay的东西(最早是用发布BSD Unix),从伯克利的文化风格来讲,RISC-V采用BSD也算是情理之中。

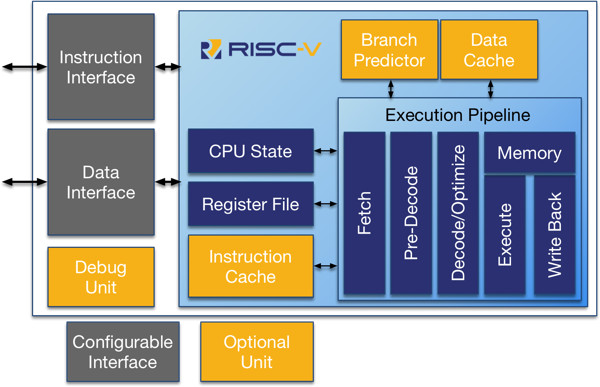

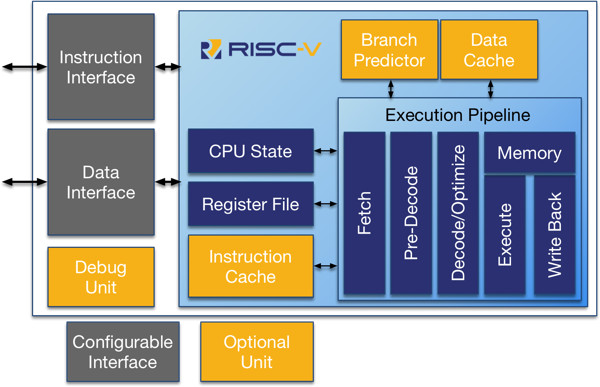

2、更小更精,模块化

RISC-V基础指令集则只有40多条,加上其他的模块化扩展指令总共几十条指令。

目前的“RISC-V架构文档”分为“指令集文档”(riscv-spec-v2.2.pdf)和“特权架构文档”(riscv-privileged-v1.10.pdf)。“指令集文档”的篇幅为145页,而“特权架构文档”的篇幅也仅为91页。相对上手和入门较快。

RISC-V架构不仅短小精悍,而且其不同的部分还能以模块化的方式组织在一起,从而可以通过一套统一的架构满足各种不同的应用场景。

用户能够灵活选择不同的模块组合,来实现自己定制化设备的需要,比如针对于小面积低功耗嵌入式场景,用户可以选择RV32IC组合的指令集,仅使用Machine Mode(机器模式);而高性能应用操作系统场景则可以选择譬如RV32IMFDC的指令集,使用Machine Mode(机器模式)与User Mode(用户模式)两种模式。

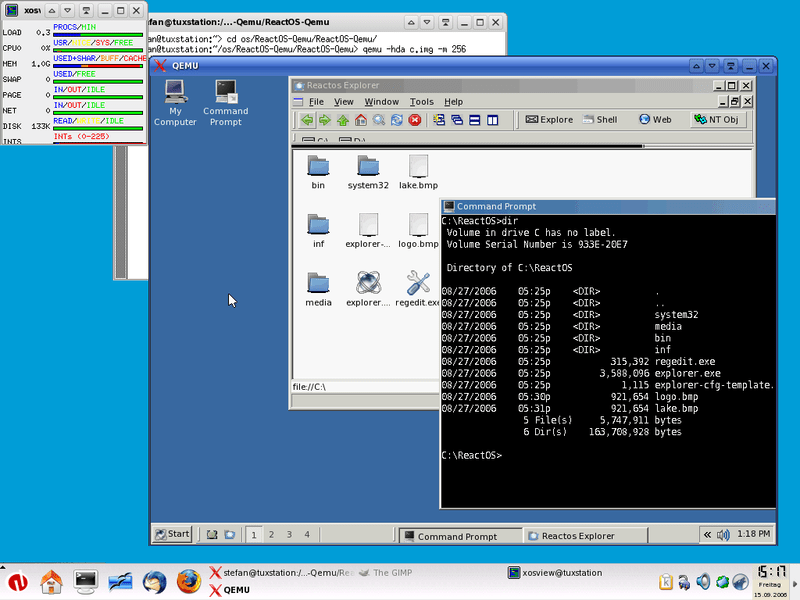

3、系统和工具链支持

从Linux 4.15内核开始,RISC-V已经获得Linux基金会和社区的支持。

软件生态方面也在逐步构建,比如调试工具链、中断控制器、JVM、LLVM、Python等开发者常用的工具都在完善之中。

此外,RISC-V还获得了Rust 语言支持。详见:https://github.com/dvc94ch/riscv-rust-toolchain(Rust 是一门由 Mozilla 开发和维护的系统编程语言。它有着惊人的运行速度,能够防止段错误,并保证线程安全)。

RISC-V Rust toolchain 的开发者还使用了由 lowRISC 基金会开发的 RISC-V LLVM 构建自己的端口,以及发布了一个 Rust 库,为 HiFive1 板提供 BSP,并为其外围设备提供支持。

×××××××××××××

相比ARM指令集,RISC-V的历史很短,2010年诞生于加州大学伯克利分校,当时的Krste Asanovic教授希望寻找一个合适的CPU指令架构,但x86架构复杂臃肿、ARM架构需要授权费、开源的OpenRISC架构又太老旧了,所以他最终决定自己做个开源CPU架构,在2015年最终成立了RISC-V基金会,专门推动RISC-V发展。

现在的RISC-V基金会成员也扩大到了80多人,包括Google、HP、Oracle、西数等公司都开始支持RISC-V架构。而且国内的公司也开始积极参与 RISC-V 生态系统,2018年 10 月份在中国上海成立了中国 RISC-V 产业联盟,包括芯原微电子、北京君正、安徽华米、上海小蚁、苏州国芯、紫光展锐等公司也加入了 RISC-V 联盟。

在美国,已经有不少知名高校开始把原本使用的MIPS指令集启蒙教材换成RISC-V了。更瞩目的是在软件业发达的印度,已经将RISC-V列为国家标准指令集。

也许未来五年,IoT领域依然是ARM的天下,但五年后呢?

现在你们知道ARM为啥紧张了吧?

作者:长空无名

来源:IoT前哨站

本文相关引用:

《大道至简——RISC》

https://wallstreetcn.com/articles/3280667

《什么是RISC-V》

https://zhuanlan.zhihu.com/p/49176102

《ARM 授权费用太贵 科技巨头欲转向开源架构 RISC-V》

https://www.leiphone.com/news/201805/8Nubo2qqdS7P8YRD.html